100Gイーサネットの理解

100Gイーサネットは現在増加中していますが、100Gイーサネットとは実際のところ何を意味しているのでしょう? CFP、CXP、QSFP28、10x10、4x25、SR4、LR4、FEC、非FEC...といった色々な名称が出てきます。 私たちはこの記事で掘り下げて、その組み合わせとこの分野で実際に展開されているものについて説明します。

100Gのフォームファクタ

100Gの世界への最初の一歩は下図で示されたフォームファクタを理解することです。

CFP 100G 光トランシーバ

まずはCFP (C Form Factor Plugable, 「着脱可能Cフォームファクタ」) を取り上げます。 (Wikipedia) CFPは物理的に巨大なため、光トランシーバの第一波において利用されました。そのモジュールが多くの電力を消費することを可能としつつ、PHY、Gearbox、リタイマーおよび他のICのための十分な空間があります。これらはバックボーンに配置され、極めて高価です。モジュール1つにつき50,000ドルから100,000ドルと考えてください。内部には10の10Gレーンをもっています。

100G CFP SR10/LR10のメリットとは、文字通りSR (短距離) およびLR (長距離)ともに10の10Gレーンをもっていることです。このように、迅速なデプロイを可能とするために既存の10G技術全てが再利用されています。これの主な使用事例は通信事業者による100G LR10接続です。

CFP2とCFP4 100G 光トランシーバ

CFP2と後継のCFP4は次なる進化でした。CFP2は10x10Gおよび新しい4x25G接続の両方をサポートされています。フォームファクタのサイズは大きく縮減され、最大電力消費も削減されました。しかし、CFP4はCFP2よりも小さいと同時にQSFP28ポートに似ています。CFP4とQSFP28のフォームファクタは異なっており、互換性はありません。電力消費とピン配列は著しく異なっています。CFP4はモジュール1つにつき10Wを割り当てます。たとえば1Uの中に48 x 100Gポートあるような高いポート密度の100Gスイッチに電力供給することについて考えると、これは極めて高い数値です。

CXP 100G 光トランシーバ

CXPが面白いインターフェイスであるのは、その主な用途がHPCへの100G SR10での接続である点です。たとえばラック内のコンピュート/ストレージクラスタの接続に利用されています。SR10にのみ焦点を当てているため、その所要電力はずっと低く、フォームファクタも小さくてコンパクトになっています。この規格は主にMellanoxによって同社InfiniBandのNIC及びスイッチの領域で推し進められました。

QSFP28 100G 光トランシーバトランシーバ -- 勝者

そしてついにQSFP28です。これが現在 (2016/6) の最も重要な100Gの規格であり、将来においてもそうであるというのが私たちの考えです。MPO12ケーブルコネクタを使用しており、フォームファクタ/ピン配列は40G QSFP+インターフェイスと全く一致しています。これが支配的なフォームファクタとなるのはなぜでしょうか? 同様の理由で、1G SFPは10G SFP+となります。ケーブリングタイプはQSFP+ 40Gと同一であり、トランシーバのピン配列は同じで、そのスイッチベンダは種々のポートサイズを備える代わりに高密度の40G/100Gデュアルモード・ポートを備えています。ちょうど私たちがいま取り上げたSFP/SFP+ 1G/10Gポートのようなものです。

100Gケーブリング+コネクタ

100Gのケーブリングおよびコネクタは極めて単純です。これについての最も簡単な考え方は、100G LRについては何も変わりません。しかし、100G SRのデュプレックスLC MMFファイバであった全てのものは現在、マルチモードのOM3/OM4ファイバーをもつMPO12コネクタです。

LC/SC 長距離 100G LR4/LR10 -- 変更なし

ケーブリングは100Gの世界の光トランシーバよりもずっと単純です。100G LR4 / LR10にとって本当に何も変わらないのは、 その光トランシーバが (物理的にファイバーを分離する代わりに) 光波長に基づいてレーンを分けているからです。100GシングルモードSCあるいはLCコネクタは、その1G / 10G / 40Gの片割れと一致しています。左図はデュプレックスLCおよびデュプレックスSCコネクタをもつ100Gシングルモードケーブルの一例です。最大伝送距離はLR4で10Km、ER4では40Kmとなっています。

MPO24 短距離 100G SR10

MPO24のケーブリングは100G SR10接続について主にCXP HPCクラスタのために利用されます。24に分離したファイバーがあり、それがこのケーブルの製造費をいくらか高額にしています。この種のケーブルを見つけることほとんど稀で、100G SR10規格は徐々に消えて行き、100G SR4に取って代られるでしょう。このフォーマットに何らかの投資をすることは全く良くない考えでしょう。

MPO12 短距離 100G SR4 -- 勝者

100G短距離についてMPO12ケーブリングが圧勝しています。それは40G SR4コネクタおよびケーブリングと全く一致しているので、全面的に100Gにする総額はやや高くなるかもしれませんが、40G MPO12へとケーブリングとパッチパネルを更新できます。そしてその100Gの価格設定が下がったとき、仮にデュアルモード40G/100Gスイッチを買ってていたならば、必要なことはその光トランシーバを100Gへと更新することだけです。

100Gのプロトコル

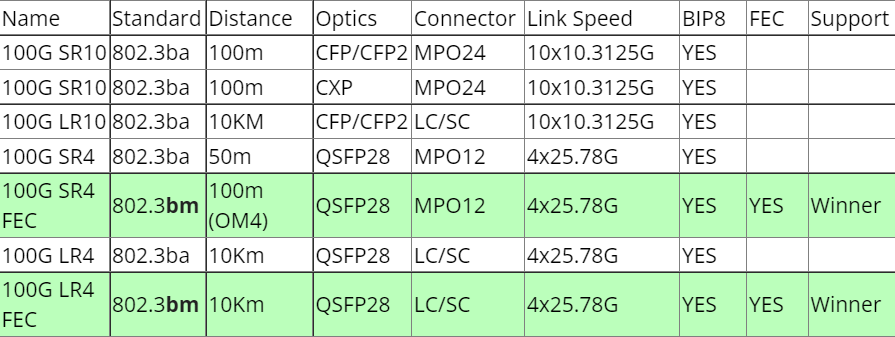

100Gのためのプロトコルはいくらか分かりづらいです。その候補となるものは、SR10、LR10、SR4、LR4、SR4 FEC、LR4 FECで、これが事態をややこしくしています。これらのプロトコルは全て、100.00Gbpsのデータ転送速度と148.88Mppsのパケット転送速度をもつ受信/送信イーサネットポートを提供しています。(私たちが現在1秒ごとに148,880,000パケットを扱っていることを恐ろしいと思わないなんて超現実的なことです!)

しかし各プロトコルがどのようにエンコードされ、最後のビットがそのパイプを降りてくるのが実際にどう見えるかに関しては多くの違いがあります。より高いレベルで種々のプロトコルについて掘り下げてみましょう。

10の10Gレーン

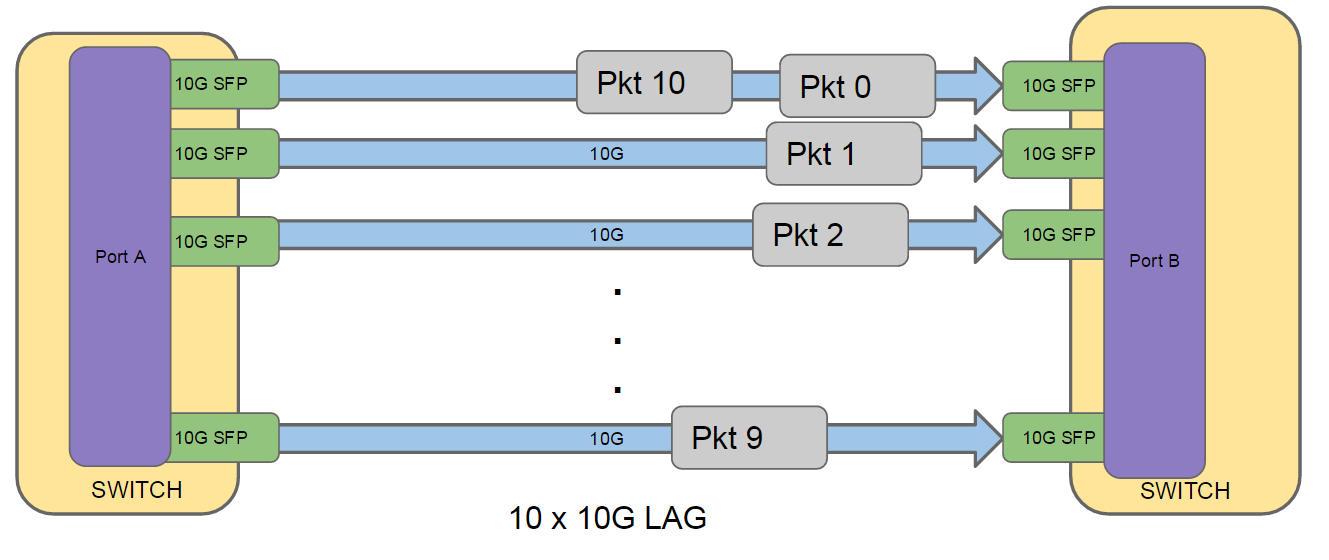

10の10Gレーンを利用するのは100Gbpsの接続を達成する最も容易な方法です。最初に明確にしなければならないことは、「100G LR10/SR10 != 10 x 10G LAG接続」ということです。そのプロトコルは著しく異なっています。

上はLAGの典型的なセットアップがどうなっているかを示しています。これは原則的にスイッチの間でNのリンクを単一の仮想ポートへと結合しています。データ伝送に関して標準的な10GBASER SR/LRの上を流れていますが、論理的には事実上100Gポートです。この場合、 全くの下方にある各接続において、それはラウンドロビン・スケージューリングのパケットです。ここでの問題は受信側のパケットが異常な状態で到達しうるということです。レーン0にある1500Bのパケットと、レーン1にある64Bのパケットを想像してみましょう。64Bの最後のバイトは1500Bのパケットの最後のバイトより前に到達するでしょう。LAGプロトコルはこれを解決する方法を有していますが、一般的に100Gについて話すとき、それは10x10G LAG接続を意味していません 。

次に真の100G SR10 / LR10インターフェースを取り上げます。下の図表から、「100G SR10 != 10 x 10G SR LAG リンク」だと明確なはずです。

上の図で見られる通り、パケットは全レーンにわたってストライプ状になっており、特に64b/66bでエンコードされたチャンクであるため、順序に関する問題は起こりません。100Gプロトコルはアライメントマーカーを用いたレーン・デスキューを含んでいます。これは、パケットが再構築されてMACに送信される前に受信側が正確にビットを整列できることを意味しています。またそれはそのプロトコルに組み込まれたエラーの検出 (ただし訂正ではない) を提供するBIP8プロトコルも含んでいます。

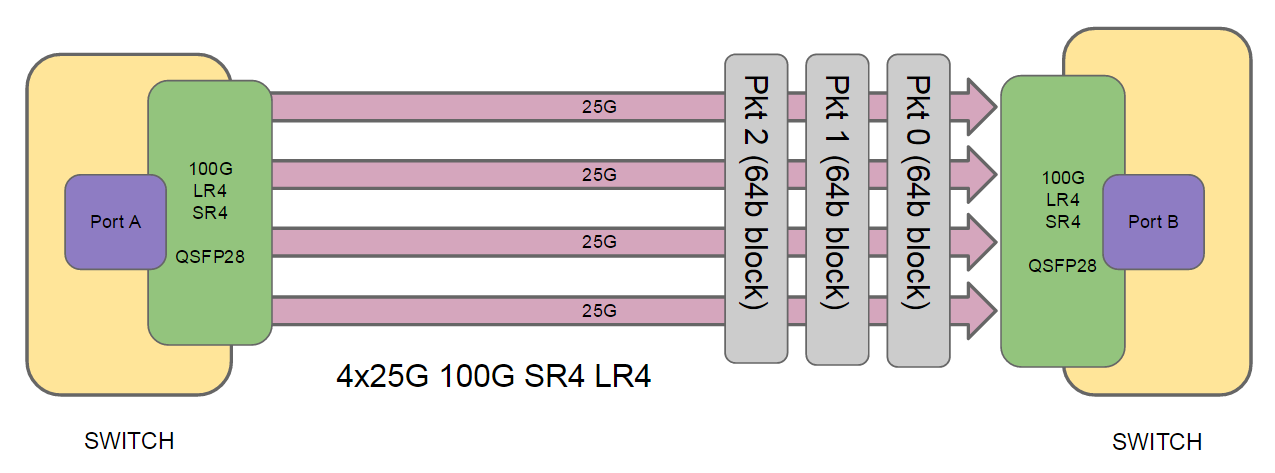

4つの25Gレーン

次にSR4/LR4を取り上げます。それは各25Gの4レーンです。より正確にはエンコーディングのオーバーヘッドのため、4 x 25.78125Ghzとなります。それもまた接続全てを送信する前にパケットを64b/66bブロックへとストライプ状にし、BIP8エラー検出 (注意: エラー検出は訂正ではありません) を含んでいます。しかしながらここにクセがあり、 4x25G接続には実際には2つの異なる規格が存在します。IEEE 802.3 baとIEEE 802.3 bmです。

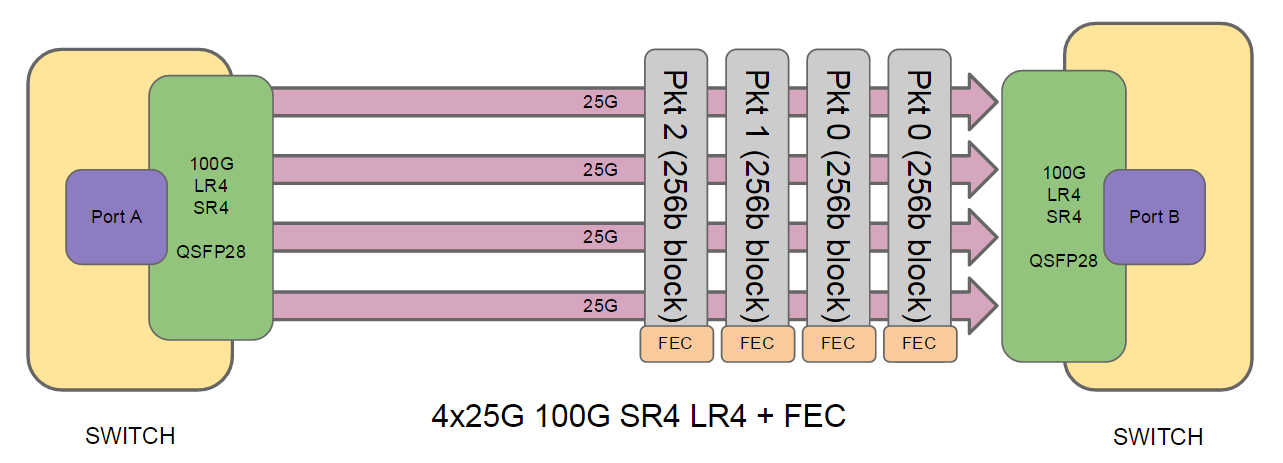

4つの25Gレーン + FEC

そして最後には、業界が集中している100G QSFP28 4x25G+FECです。802.3baと802.3bmの違いは、FEC (Forward Error Correction, 前方誤り訂正) です。これはそのストライプのサイズを64bから256bに変更し、リードソロモン誤り訂正のパリティブロックを追加しています。それはECC RAMが動作する方法と非常に似ており、 同様の計算を利用しているがわずかに異なるパラメータを用いています。それをECCシリアルリンクと考えましょう。それゆえ、802.3bmによってその受信側はビット誤りを検出できるのみならず、ビット誤りを訂正してそのリンクの品質を大幅に改善することができるのです。

要約

私たちの考えでは、QSFP28 SR4/LR4にFECを加えたものが支配的な100G規格となるでしょう。全てのスイッチベンダはFECをサポートしており、より短距離のSR4またはLR4にとって必須ではないものの、FECがデフォルトの状態で全ての100Gリンク上で使用可能になるだろうと私たちは確信しています。QSFP28光トランシーバは、スイッチベンダをシングルポート・マルチモード40G/56G/100G QSFP/QSFP28の物理的なケージへと進ませながら、利用可能性と価格設定の面で向上しています。

100Gイーサネットの分裂はついに収束し始めています。ここまで来るのに長い年数がかかり、全ての人が100Gbpsのネットワークをリーズナブルな価格で享受するため、残る課題はコストを下げることのみです。

次に、100G SR4/LR4+FEC規格を深く掘り下げ、どう作動するかの全てを詳細に説明します。