10G Layer1 Packet Capture

Sometimes 10G Packet Capture is not enough, whats really required if 10G Layer 1 Packet Capture. Mind you its not really packet capture at that level but a stream of XGMII data on the wire.

FMADIO Layer 1 Packet Capture is very basic, we built in a small XGMII Capture block into our FPGAs when developing the network interface block. As its very helpful for us when debugging Layer 1 Network problems, maybe you can find utility in it too.

XGMII Packet Capture

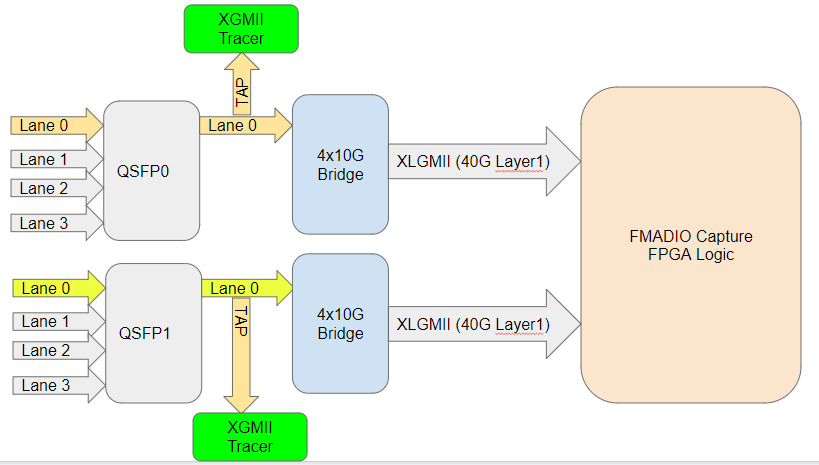

The trace logic is really small, total of 256 x 64bit data + 8bit control XGMII cycles. By default its only on Lane 0 of each QSFP socket. And sufficient for a few packets, usually thats enough to get that Ahah moment the Start of Frame marker is byte swaped. Its literally the XGMII Control and Data without any packet framing.

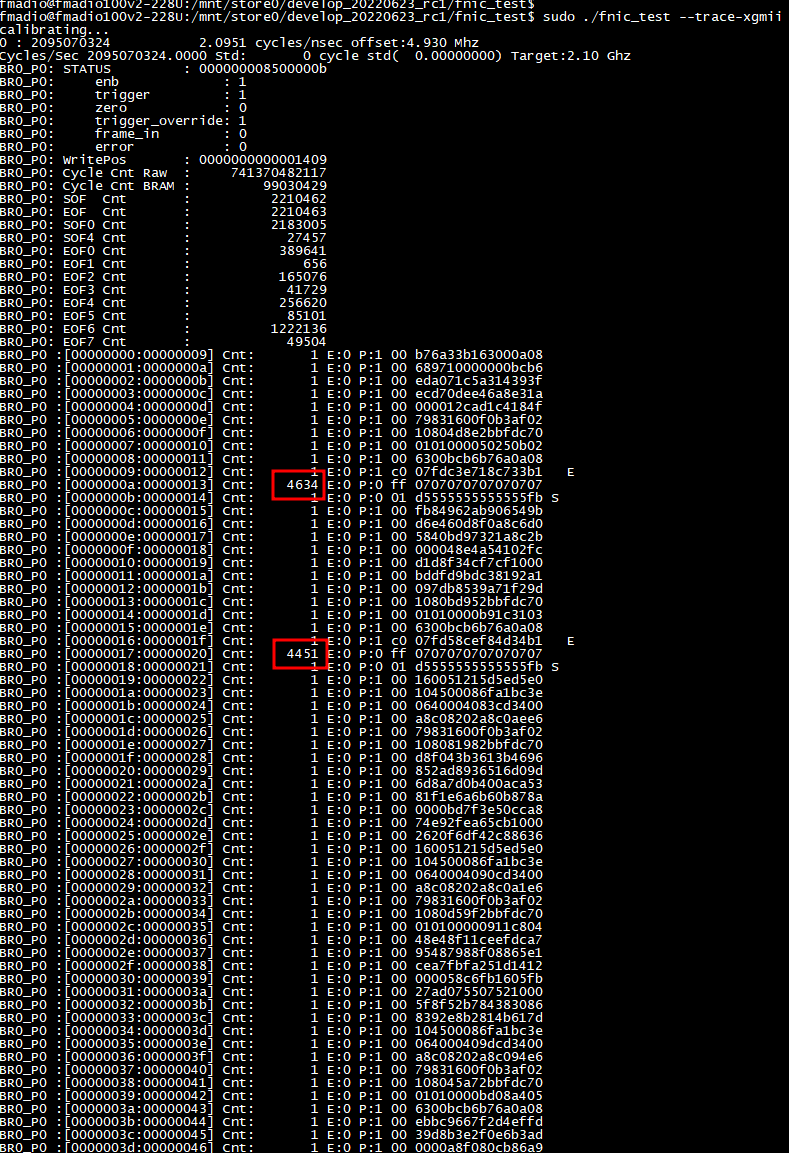

Because most of the time the XGMII link is idle, we added a delta compression scheme to the output. e.g. if the previous cycles control/data is the same as this cycles control/data then increment a Run Length Encode like counter. Can see that in the below image

FMADIO Layer 1 Capture

In the above we see the XGMII Idle cycles repeated 4634 and 4451 times between 2 separate packets.

Its not a complete Layer 1 Packet Capture appliance … yet. This function is available on all FMADIO 40Gbps and FMADIO 100Gbps capture systems. Maybe its helpful for some basic debugging of Layer 1 Packet Corruption problems.

As always contact us for any questions!